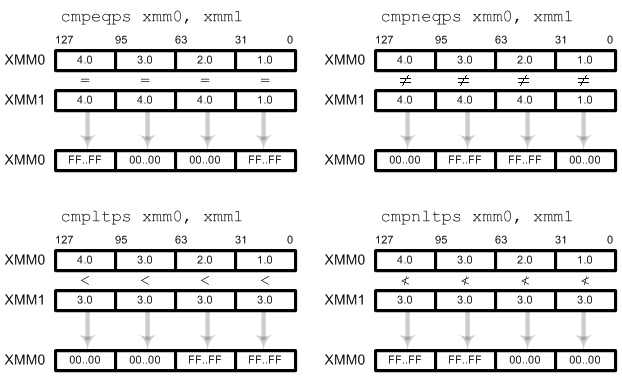

The basic single precision FP comparison instruction is similar to existing MMX instruction variants: it produces a redundant mask per float of all 1?s or all 0?s, depending upon the result of the comparison. This approach allows the mask to be used with subsequent logic operations (AND, ANDN, OR, XOR) in order to perform conditional moves.

CMPPS (parallel) and CMPSS (scalar) compare the pair of operands using the immediate operand as a predicate, returning an all “1” 32-bit mask or an all “0” 32-bit mask as a result. This instruction supports a full set of 12 conditions: equal, less than, less than equal, greater than, greater than or equal, unordered, not equal, not less than, not less than or equal, not greater than, not greater than or equal, ordered.

COMISS and UCOMISS compare the least significant pair of operands and sets the ZF, PF and CF bits in the EFLAGS register.